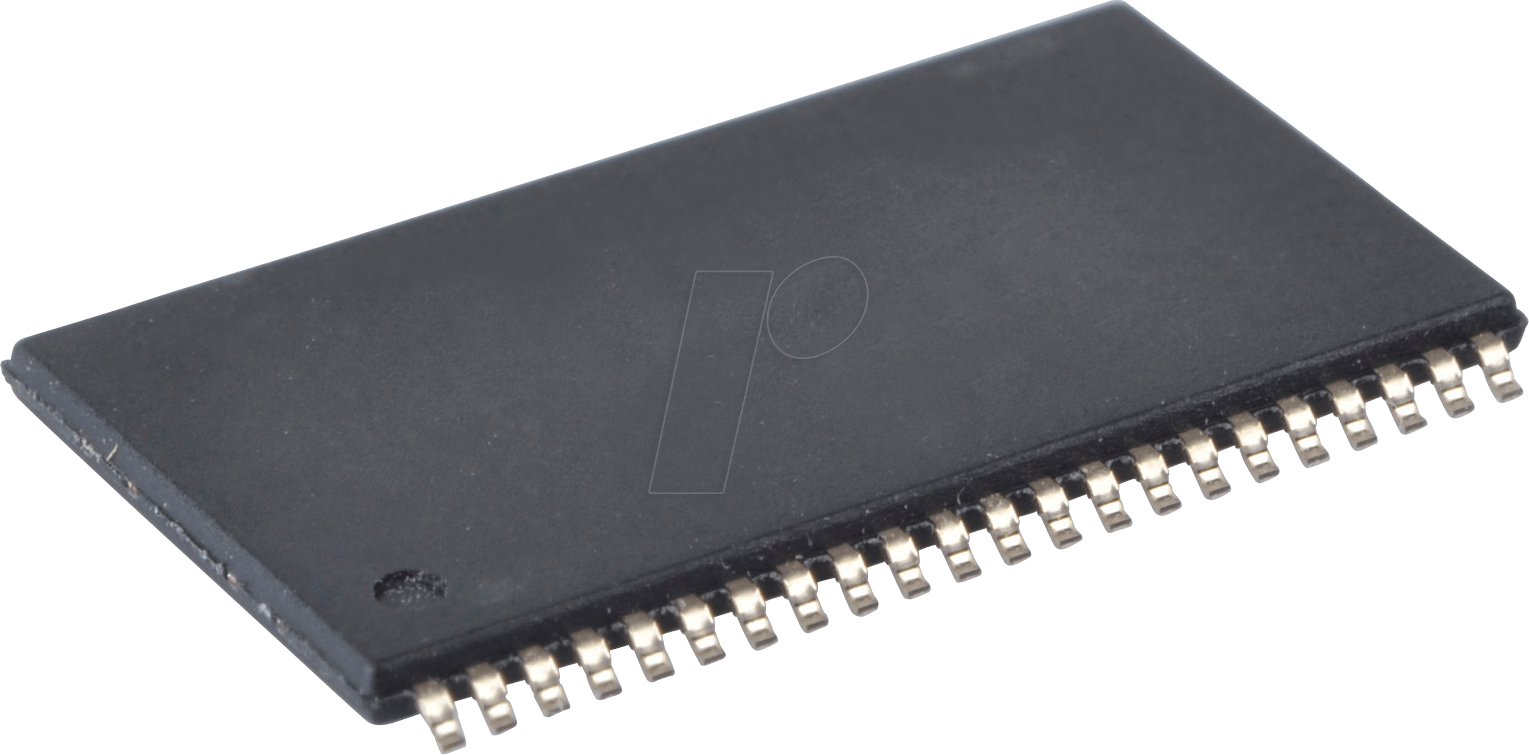

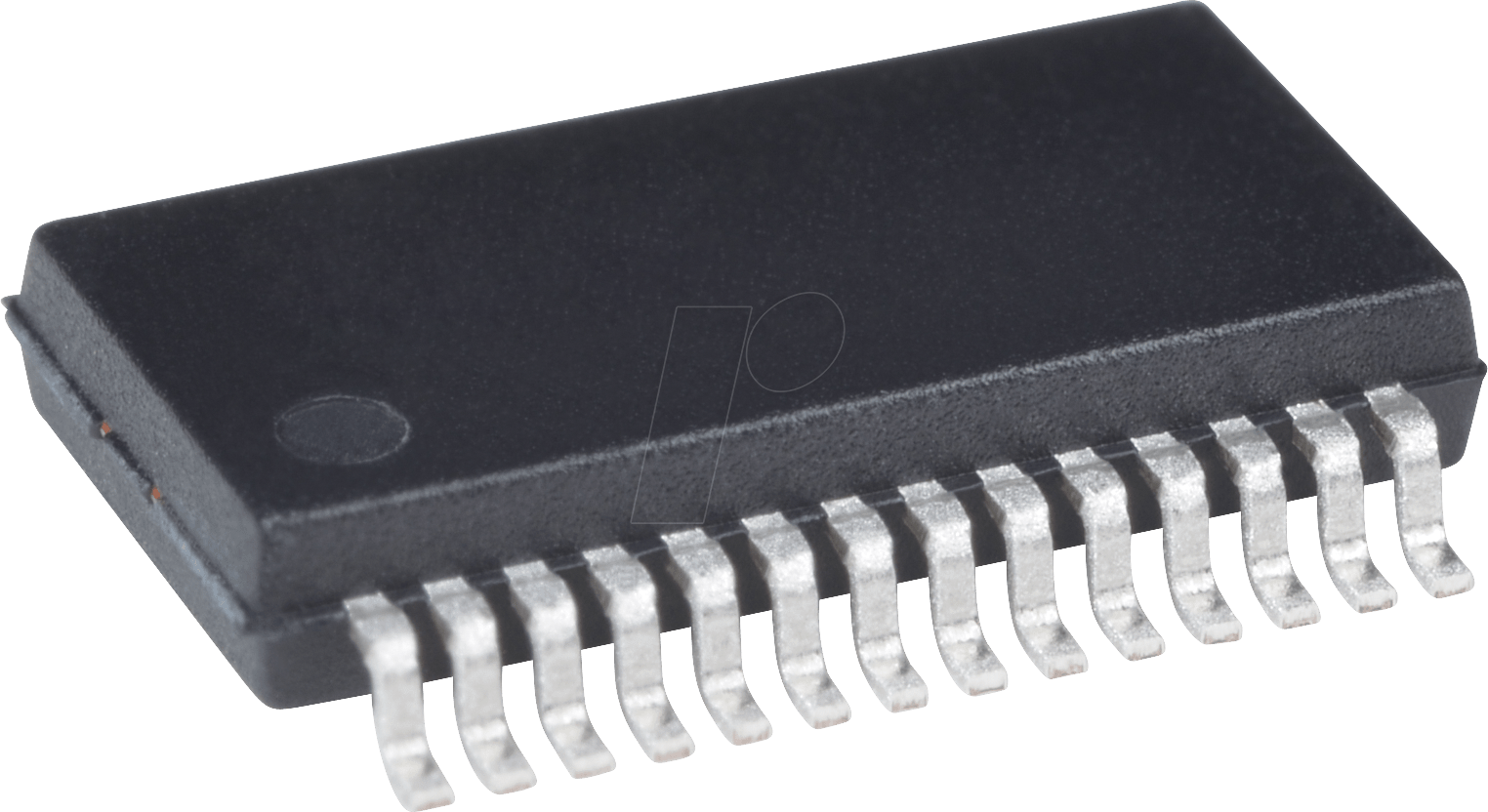

CY62167G-45ZXI - SRAM, 16 Mb (2 M x 8/ 1 M x 16 ), 5 V, 45ns, TSOP-48

28,50 €

16-Mbit (1Mb × 16-bit/2Mb × 8-bit) Statisches RAM mit Fehlerkorrekturcode (ECC)BeschreibungCY62167G und CY62167GE sind hochleistungsfähige CMOS-SRAM-Bausteine mit niedrigem Stromverbrauch (MoBL®) und eingebettetem ECC[1]. Beide Bausteine werden in Single- und Dual-Chip-Enable-Optionen und in Mehrfach-Pin-Konfigurationen angeboten. Der Baustein CY62167GE enthält eineERR-Pin, der ein Einzelbit-Fehlererkennungs- und Korrekturereignis während eines Lesezyklus signalisiert. Um auf Geräte mit einem einzigen Chip-Freigabeeingang zuzugreifen, setzen Sie den Chip-Freigabeeingang (CE) auf LOW. Um auf Dual-Chip-Freigabegeräte zuzugreifen, müssen beide Chip-Freigabeeingänge aktiviert werden - CE1 als LOW und CE2 als HIGH. Um Datenschreiboperationen durchzuführen, setzen Sie den Write Enable (WE)-Eingang auf LOW und stellen die Daten und die Adresse an den Datenpins (I/O0 bis I/O15) bzw. Adresspins (A0 bis A19) des Geräts bereit. Die Eingänge Byte High Enable (BHE) und Byte Low Enable (BLE) steuern Byte-Schreiboperationen und schreiben Daten auf den entsprechenden E/A-Leitungen in die angegebene Speicherstelle. BHE steuert I/O8 bis I/O15 und BLE steuert I/O0 bis I/O7. Um Daten zu lesen, aktivieren Sie den Eingang Output Enable (OE) und geben Sie die erforderliche Adresse auf den Adressleitungen an. Sie können auf Lesedaten auf den E/A-Leitungen (I/O0 bis I/O15) zugreifen. Um Byte-Zugriffe durchzuführen, setzen Sie das erforderliche Byte-Freigabesignal (BHE oder BLE) ein, um entweder das obere oder das untere Datenbyte von der angegebenen Adressposition zu lesen. Alle E/As (I/O0 bis I/O15) werden in einen hochohmigen Zustand versetzt, wenn der Baustein abgewählt wird (CE HIGH für einen Single-Chip-Freigabebaustein und CE1 HIGH / CE2 LOW für einen Dual-Chip-Freigabebaustein), oder die Steuersignale deaktiviert werden (OE, BLE, BHE). Diese Bausteine verfügen über eine einzigartige Byte-Power-down-Funktion, bei der die Bausteine, wenn beide Byte-Freigaben (BHE und BLE) deaktiviert sind, unabhängig vom Zustand der Chip-Freigaben nahtlos in den Standby-Modus wechseln und dadurch Strom sparen. Bei den CY62167GE-Bausteinen wird die Erkennung und Korrektur eines Einzelbitfehlers an der Stelle, auf die zugegriffen wird, durch die Behauptung des ERR-Ausgangs (ERR = High) angezeigt. Die Bausteine CY62167G und CY62167GE sind in einerPb-freie 48-polige TSOP I-Gehäuse und VFBGA-Gehäuse mit 48 Kugeln.Merkmale• Ultra-niedriger Standby-Strom - Typischer Standby-Strom: 5,5 µA - Maximaler Standby-Strom: 16 µA• Hohe Geschwindigkeit: 45 ns/55 ns• Eingebetteter fehlerkorrigierender Code (ECC) für Einzelbit-Fehlerkorrektur• Großer Spannungsbereich: 1,65 V bis 2,2 V, 2,2 V bis 3,6 V und 4,5 V bis 5,5 V• 1.0-V-Datenspeicherung• Transistor-Transistor-Logik (TTL)-kompatible Ein- und Ausgänge• Fehleranzeige-Pin (ERR) zur Anzeige der 1-Bit-Fehlererkennung und -Korrektur• 48-poliges TSOP I-Gehäuse, konfigurierbar als 1M × 16 oder 2M × 8 SRAM• Erhältlich in Pb-freiem 48-Ball VFBGA und 48-Pin TSOP I Gehäuse

Deine Shops für beste Deals

reichelt elektronik

Logge dich ein für Coupon Details