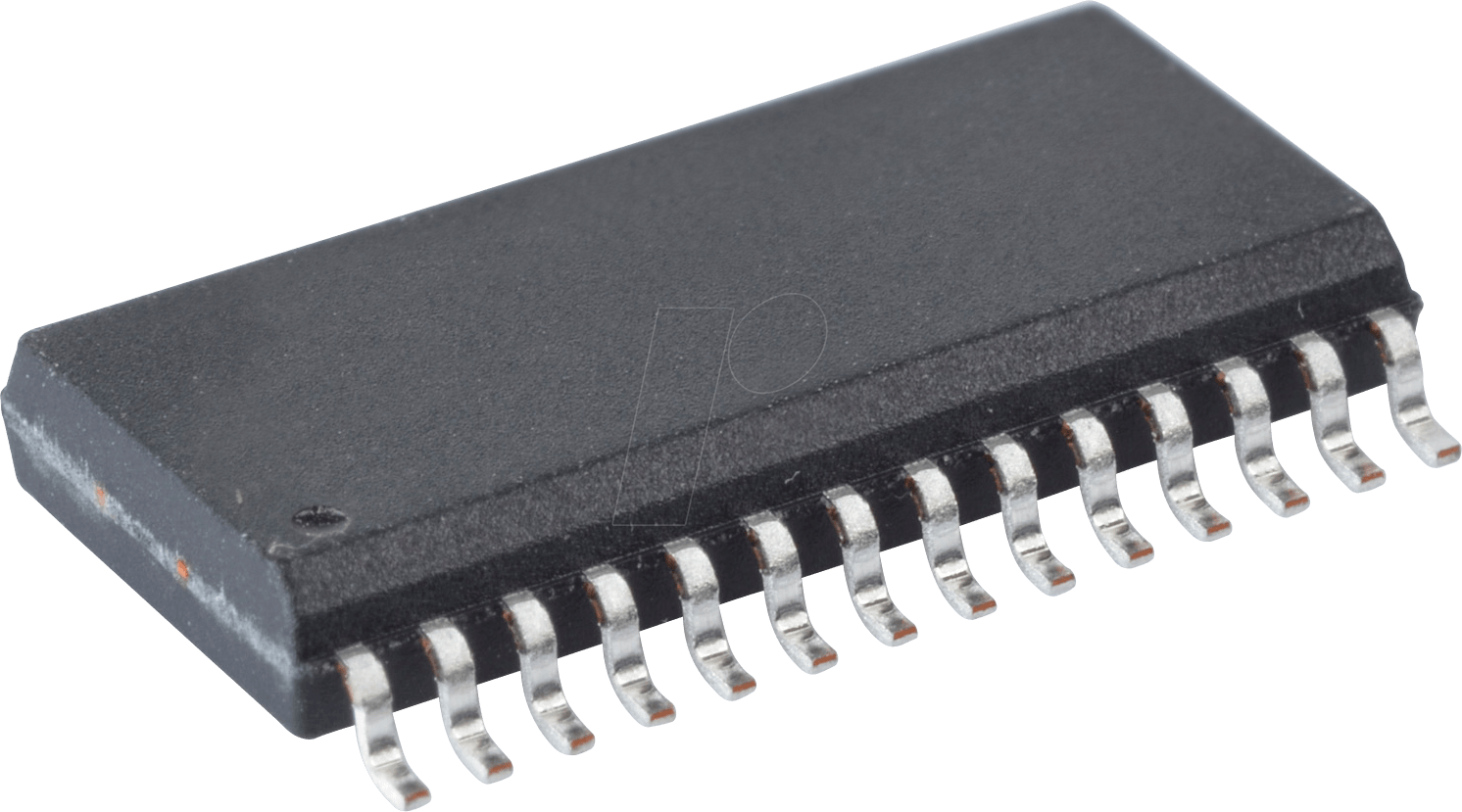

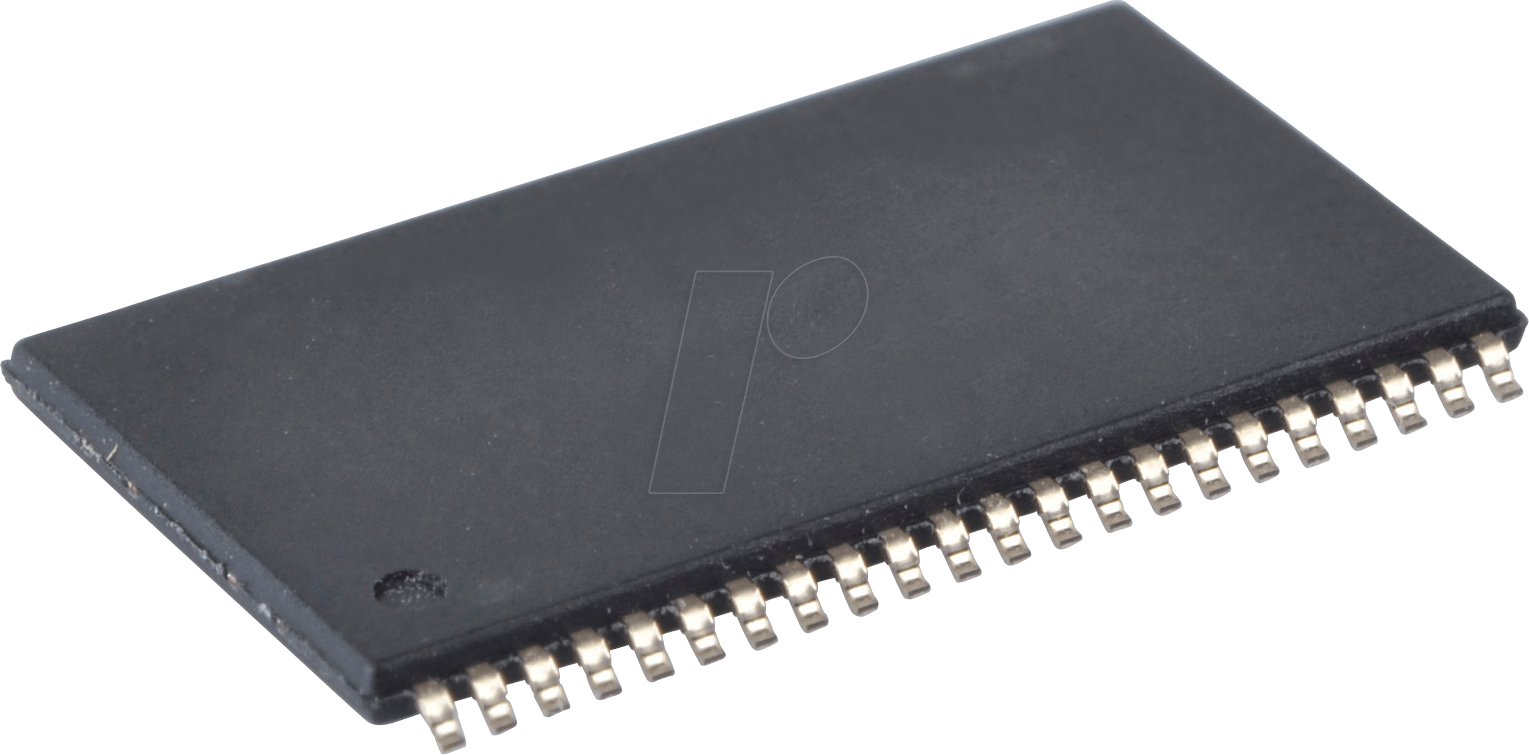

CY7C1021D-10ZSXI - High-Speed SRAM, 1 Mb (64 K x 16), 5 V, 10ns, TSOP-44

High-Speed CMOS Static RAM 5V 64kx16 10ns TSOP44(II)Funktionale Beschreibung:Der CY7C1021D ist ein hochleistungsfähiger stati... Mehr erfahren

Produktvarianten

CY7C1021D-10ZSXI - High-Speed SRAM, 1 Mb (64 K x 16), 5 V, 10ns, TSOP-44

Finde die besten Angebote

Bester Preis1 Punkte

reichelt elektronik

Versand: 5,95 €

Lieferzeit: 1-3 Werktage

Versand: 5,95 € | Lieferzeit: 1-3 Werktage

Ähnliche Produkte

Produktdetails

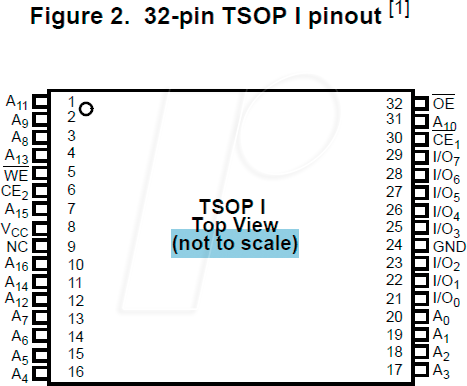

High-Speed CMOS Static RAM 5V 64kx16 10ns TSOP44(II)Funktionale Beschreibung:Der CY7C1021D ist ein hochleistungsfähiger statischer CMOS-RAM, der als 65.536 Worte mit 16 Bit organisiert ist. Dieser Baustein verfügt über eine automatische Abschaltfunktion, die bei Abwahl den Stromverbrauch erheblich reduziert. Die Eingangs- und Ausgangspins (I/O0 bis I/O15) werden in einen hochohmigen Zustand versetzt, wenn der Baustein abgewählt wird (CE HIGH), Ausgänge deaktiviert werden (OE HIGH), BHE und BLE deaktiviert werden (BHE, BLE HIGH) oder während eines Schreibvorgangs (CE LOW und WE LOW). Schreiben auf das Gerät unter Verwendung der Eingänge Chip Enable (CE) und Write Enable (WE) LOW. Wenn Byte Low Enable (BLE) LOW ist, dann werden Daten von I/O-Pins (I/O0 bis I/O7) an die auf den Adresspins (A0 bis A15) angegebene Stelle geschrieben. Wenn Byte High Enable (BHE) LOW ist, dann werden Daten von I/O-Pins (I/O8 bis I/O15) an die auf den Adresspins (A0 bis A15) angegebene Stelle geschrieben. Lesen Sie aus dem Gerät, indem Sie Chip Enable (CE) und Output Enable (OE) LOW nehmen, während Sie Write Enable (WE) HIGH erzwingen. Wenn Byte Low Enable (BLE) LOW ist, erscheinen Daten von der durch die Adresspins spezifizierten Speicherstelle auf I/O0 bis I/O7. Wenn Byte High Enable (BHE) LOW ist, erscheinen Daten aus dem Speicher an I/O8 bis I/O15. Eine vollständige Beschreibung der Lese- und Schreibmodi finden Sie in der Wahrheitstabelle auf Seite 10. Der Baustein CY7C1021D eignet sich für den Anschluss an Prozessoren mit TTL-I/P-Pegeln. Er eignet sich nicht für Prozessoren, die CMOS-I/P-Pegel benötigen.Merkmale:• Temperaturbereiche: Industriell: -40 °C bis 85 °C• Pin und Funktion kompatibel mit CY7C1021B• Hohe Geschwindigkeit: taa = 10 ns• Niedrige Wirkleistung: Icc = 80 mA bei 10 ns• Niedrige CMOS-Standby-Leistung: Isb2 = 3 mA• 2,0 V Datenspeicherung• Automatisches Ausschalten bei Abwahl• CMOS für optimale Geschwindigkeit und Leistung• Unabhängige Kontrolle der oberen und unteren Bits• Erhältlich in Pb-freien 44-poligen 400-Mil Wide Molded SOJ und44-poligem TSOP-II-Gehäuse

Informationen

Lieferzeit:1-3 Werktage

Marke:Cypress